| Sprog : |

|

| Encyclopedia samfund |Encyclopedia Svar |Indsend spørgsmål |Ordforråd Viden |Upload viden |

En cache |

|

|

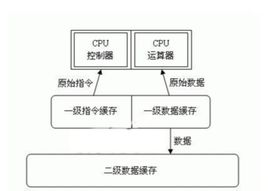

Har indbygget CPU cache inde i CPU'en og kører med samme hastighed, effektivt kan forbedre effektiviteten af CPU. Niveau cache, jo højere virkningsgrad af CPU, men er begrænset af den indre struktur af CPU, cache kapacitet er meget lille. Kort introduktion CPU cache (Cache Memory) er placeret mellem CPU og hukommelse midlertidig hukommelse, hvilket er meget mindre end hukommelseskapacitet af valutakursen, men meget hurtigere end hukommelsen. Cache synes primært at løse CPU-hastighed og hukommelse adgang hastighed mismatch modsigelse, da CPU-hastighed er meget hurtigere end at læse hukommelse og skrive hastigheder, ville det tage en CPU ventetid data ankomst eller at skrive data til hukommelsen . Data i cache-hukommelse i en lille del, men det er en lille del af det forestående besøg af en kort CPU, når CPU'en kalder en masse data, kan du undgå opkaldet direkte fra cache-hukommelse til at fremskynde læse hastighed . Således er cachen i CPU tilsættes til en effektiv løsning, således at hele hukommelse (cache-hukommelse ) blev både den høje hastighed cache, men også en stor hukommelseskapacitet lagersystemet. CPU cache stor indflydelse på resultater, hovedsagelig på grund af den båndbredde af CPU og dataudveksling sekvens mellem CPU og cache forårsaget.Princip Caching arbejder, når CPU til at læse en data først ser ud fra cachen, hvis det findes straks læse og sendt til CPU, Hvis den ikke findes, er det læses fra hukommelsen med en forholdsvis langsom hastighed og gav processorkraft mens datablokken hvor overførte data til cache, så du senere kan læse data på det hele udføres fra cachen, uden at skulle påberåbe hukommelsen. Det er denne mekanisme gør det muligt for CPU'en at læse read cache hit rate er meget høj (det meste af CPU op til omkring 90%), dvs 90% af CPU-tid til at læse de næste data i cachen, kun omkring 10% brug for at læse fra hukommelsen. Det sparer CPU-tid læses direkte i hukommelsen, men også den grundlæggende CPU læser data uden ventetid. Samlet CPU læser data sekventielt efter den første cache-hukommelse. I øjeblikket dybest set bruger SRAM cache-hukommelsen, SRAM Statisk RAM er en forkortelse af det engelske, som er en statisk access memory har en funktion, det vil sige ikke brug for en opdatering kredsløb, der kan lagre data internt lagret. I modsætning til DRAM hukommelse refresh kredsløb efter behov, med mellemrum, fastsat til en enkelt gebyr for DRAM refresh, ellers de interne data vil forsvinde, så SRAM har højere ydelse, men SRAM har også sine ulemper, nemlig dens integration lavere, kan den samme kapacitet DRAM hukommelse være udformet som et mindre volumen, men det kræver en masse volumen SRAM, som i øjeblikket ikke cache kapacitet til at gøre meget af de vigtige grunde. Dens kendetegn er opsummeret som følger: den fordel, at energibesparelser, høj hastighed, ikke passer hukommelsen refresh kredsløb, kan den samlede effektivitet øges, ulempen er en stor grad af integration er lav, mængden af den samme kapacitet, og prisen er høj, kun et lille beløb til nøglen at forbedre effektiviteten af systemet. Klassifikation Orden og i overensstemmelse med de data, sammenholdt med det stramme CPU, CPU-cache kan opdeles i en cache, cache, nogle high-end CPU har også en tre-niveau cache, alle data, der er lagret i cachen på hvert niveau er det næste niveau en del af cache, og de tekniske vanskeligheder af fremstillingsomkostningerne for disse tre er relativt faldende cachen, så kapaciteten er relativt forøges. Når CPU'en til at læse data, det første kig fra en cache, hvis de ikke findes så finde fra den sekundære cache, hvis du stadig ikke kan finde de tre-niveau cache eller fra hukommelsen. Generelt hvert niveau cache hit rate sandsynligvis omkring 80%, hvilket betyder at 80% af den samlede mængde data kan findes i en cache, kun 20% af den samlede mængde data, den har brug for fra den sekundære cache , tre cache eller hukommelse læse, kan vi se en hel CPU cache er en cache-arkitektur, den vigtigste del. Niveau cache (Level 1 Cache), jf. L1 Cache, ligger ved siden af CPU kerne, er mest tæt sammen med CPU CPU cache, men også historien om den tidligste CPU cache. På grund af tekniske vanskeligheder niveau cache og de højeste produktionsomkostninger, forbedre den tekniske vanskelighed bragt øget kapacitet og stigende omkostninger er meget store, men vil ikke medføre væsentlige forbedringer ydeevne, prisen er meget lav, og det eksisterende niveau cache hit har været høj, så en cache er den mindste kapacitet for alle cache, cachen er meget mindre end de to. I almindelighed kan en cache opdeles i en data-cache (Data Cache, D-cache) og en instruktion cache (Instruktion Cache, I-cache). Begge bruges til at lagre data, samt instruktion afkode data i realtid, og begge kan tilgås af CPU, reducere konflikter forårsaget af Cache påstand og forbedre processor ydeevne. I øjeblikket det meste af CPU-niveau data cache og en instruktion cache har samme kapacitet, som AMDs Athlon XP vil have en 64KB data cache og en 64KB instruktion cache, vil cachen komme til 64KB 64 KB sagde resten af CPU cache repræsentation og så videre. NetBurst arkitektur bruger CPU (den mest typiske er Pentium 4) af Intels cache er lidt speciel, en stigning i brugen af en ny trace cache (Execution Trace Cache, T-Cache eller ETC) i stedet for en instruktion cache kapacitet 12KμOps, sagde energilagring mikroinstruktion afkodet 12K af det er 12.000. Et spor cache og en instruktion cache operation mekanisme er ikke det samme, en instruktion cache til øjeblikkelig instruktion afkodning og gemmer ikke disse instruktioner, mens et spor cache også vil afkode nogle instruktioner for disse instruktion kaldet mikroinstruktion (mikro-ops), og disse kan opbevares i mikroinstruktionen niveau af spor cachen, hver gang uden at gøre dekodningsproces, og derfor et spor cache effektivt kan øge ved høj frekvens på undervisning dekoderfunktioner og μOps er mikro-ops, hvilket er betydningen af mikro-operationer. Det giver høj hastighed μops til processorkerne. Intel NetBurst mikroarkitektur hjælp henrettelse spor cache er dekoderen adskilt fra udførelse cyklus. Det spor cache UOPS med høj båndbredde til kernen væsentlige for den fulde brug af softwaren instruktion niveau parallelitet. Intel har ikke annonceret en faktiske kapacitet spor cache, bare vide, at et spor cache kan gemme 12.000 mikroinstruktion (mikro-ops). Derfor kan vi ikke bare sammenligne antallet af mikroinstruktioner instruktion cache størrelse. Faktisk er den single-core NetBurst arkitektur CPU cache hjælp 8Kμops har set nok, kan ekstra 4kμops høj grad forbedre cache hit sats. Og hvis du ønsker at bruge Hyper-Threading-teknologi, så 12KμOps vil være nogle ikke nok, hvilket er grunden til tider, når du bruger Intel-processorer Hyper-Threading-teknologi vil føre til vigtige forringelse årsag ydeevne. Northwood kerne, en buffer, såsom 8KB 12 KμOps, betyder det, dens et data cache er 8KB, et spor cache 12KμOps, mens Prescott kerne, en cache 16KB 12 KμOps, betyder det, dens en 16 KB data cache , et spor cache 12KμOps. Her 12KμOps absolut ikke lig med 12KB, enheder er forskellige, den ene er μOps, en byte (bytes), og operativsystemet mekanisme to er helt anderledes. Så dem af Intel CPU cache simpel addition, siger for eksempel Northwood kerne er 20KB cache, siges at være den Prescott kerne 28KB cache, og dermed mener Intel-processor cache kapacitet er langt mindre end 128KB af en AMD-processor cache størrelse visningen er helt forkert, de to ikke er sammenlignelige. I kontrast CPU-arkitekturer har nogle forskelle, mange har været svært at finde den tilsvarende cache noget, selv om navnet på den cache på et lignende design ideer og funktionelle definition er også anderledes, og denne gang ikke med et simpelt aritmetisk tilføjelse til at sammenligne, mens man i arkitekturen meget lig CPU sammenligning sammenligne de forskellige funktioner har visse betydning cache størrelse hhv. Action Men en stor cache og sekundære cache, hvor meget godt det vil gøre det? Du har fortalt os, at forhandlerne, i virkeligheden, er du nødt til at bruge de mest almindelige ord til at tale med ham. Så vi giver dem en analogi, siger, at det er ligesom, når du kører bil, stammen er hele sekundære cache, hvis der håndlister i en lille boks, er det dit ene cache. En god cache hvor? Hvad du føler, når du kører, som kan tages til enhver tid ting. Hvis du har en lille cache, er du nødt til at stoppe bilen, stammen til at tage tingene. Lad os først se på et simpelt cache. Mest af alt nuværende mainstream processor cache og sekundær cache med et par high-end processor integrerer også tre cache. Blandt dem kan en cache opdeles i en instruktion cache og en data cache. En instruktion cache til midlertidig opbevaring af forskellige typer aritmetiske instruktioner leveret til CPU, primære CPU data cache til midlertidig lagring af data, der er nødvendige for at levere computing, som er en cache rolle. Så den rolle sekundære cache, hvad er det? Simpelthen sat, den sekundære cache er en cache buffer: et højt niveau cache produktionsomkostninger og dermed dens begrænsede kapacitet, er den rolle sekundær cache gemt i processorkraft nødt til at bruge dem, kan de ikke gemmes i cachen oplysninger. Tilsvarende kan tre cache og hukommelse ses som to cachebuffere, deres kapacitetsforøgelse, men enheden produktionsomkostninger er aftagende. Det skal bemærkes, at hverken den sekundære cache, tre cache eller hukommelse opbevaring processor ikke kan betjene den oprindelige brugsanvisning, der kan lagres i en instruktion cache af CPU, mens de resterende sekundære cache, tre cache CPU og hukommelse til lagring kun de data, der kræves. Datacache design Afhængig af drifts-princippet, kan det nuværende niveau for mainstream processor data cache og bruges til at læse og skrive data til rigtige kode instruktion cache og data cache to slags spor, som anvendes af AMD og Intel. Forskellige krav til sekundær cache kapacitet niveau data cache design varierer også, så lad os kort se på forskellene mellem disse to primære data cache design. AMD cache design Level cache design AMD anvender en traditionel "rigtige data læse og skrive cache" design. Baseret på arkitektur niveau datacachen hovedsageligt bruges til datalagring CPU læser først, mens flere blev læst data lagret i cache og systemets hukommelse af dem. Være en simpel antagelse, hvis processoren skal læse "AMD Athlon 64 3000 ER GOD" Dette er en masse data (ikke huske den plads), så den første til at blive læst "AMDATHL" vil blive gemt i en data-cache og de resterende "ON643000 isgood" blev henholdsvis lagret i cache og system hukommelse, der (som vist nedenfor). Det skal bemærkes, at ovenstående antagelse er kun til AMD processor-level data cache en abstrakt beskrivelse af længden af de data-niveau data cache og sekundær cache kan gemmes helt bestemmes af størrelsen af cache kapacitet, men på ingen måde i ovenstående forudsætninger nogle få bytes. Fordelen ved "reelle data læse og skrive cache" er direkte læse data hurtigt, men det kræver også en vis grad af data cache kapacitet, øge vanskelighederne ved processoren (niveau datacache enhed fremstillingsindustrien koster højere end den sekundære cache ). Intel cache design Siden P4 æra begyndte Intel at bruge den nye "data kodeinstruktion trace cache" design. Denne arkitektur er baseret på den primære data cache ikke længere gemmer de faktiske data, men data er gemt i den sekundære cache instruktion kode (dvs. start adressen på de data, der er lagret i den sekundære cache). Antages processoren skal læse "INTEL P4 ER GOD" Dette er en masse data (ikke huske den plads), så alle data vil blive lagret i den sekundære cache, og en data-kode instruktion spor buffer brug for at gemme kun ovennævnte data startadresse (som vist nedenfor). Da en datacachen ikke gemmer de faktiske data, kan den "Data kodeinstruktion trace cache" design i høj grad reducere CPU datacache kapacitetsbehov, processoren mindsker vanskeligheden ved produktionen. Men ulemperne ved dette design er, at effektiviteten af data læse mere "rigtige data læse og skrive-cache design" lav og afhængig af to meget store cache kapacitet. |

| Bruger Anmeldelse |

|

Ingen kommentarer endnu |